# 海洋レーダ送受信機の FPGA 向けディジタルフィルタ実装と最適化

櫻本 大翔

長名 保範

藤井 智史

石垣 善教

琉球大学大学院理工学研究科 熊本大学半導体・デジタル研究教育機構 琉球大学/ORNIS 株式会社 ORNIS 株式会社

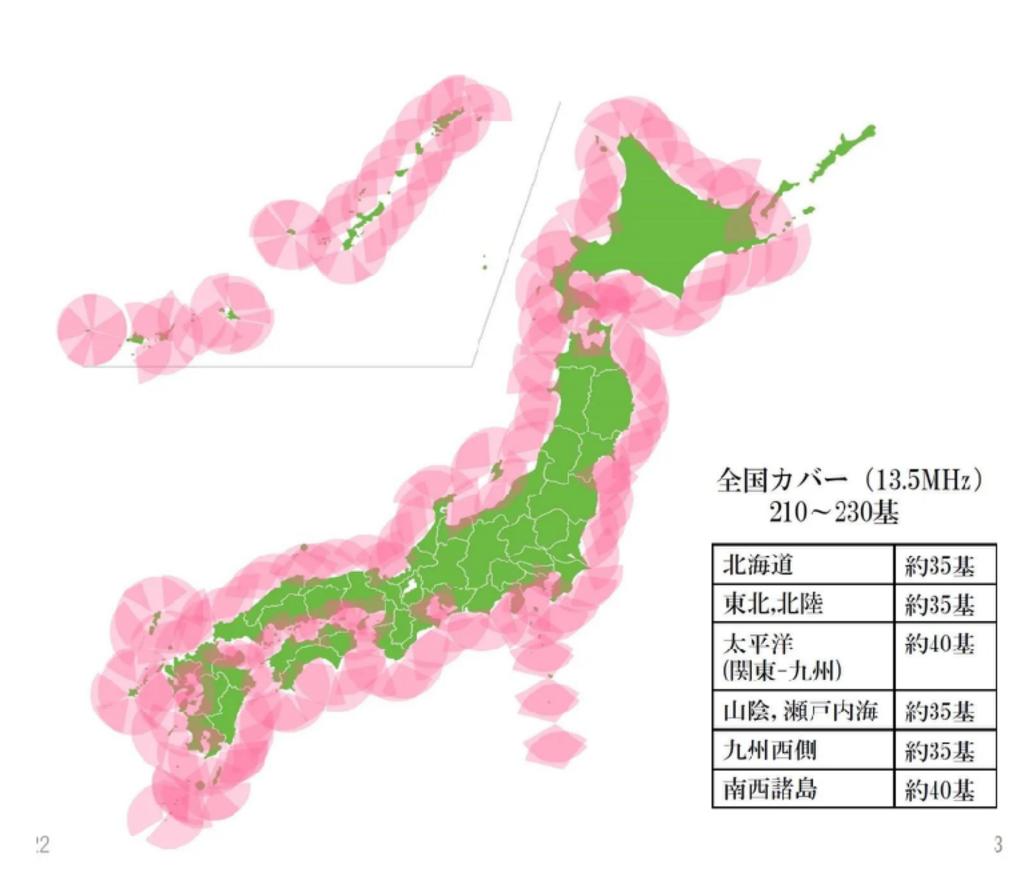

#### 背景

- ・海洋レーダ網の全国展開

- ・ 全国をカバーするために

- ・13.5MHz のレーダが 210~230基必要

- ・ 低価格な海洋レーダの開発が必須

- FPGA ボードを用いたディジタル実装

https://www.ornis.jp/technology

# 各し一岁局

- ・国内数力所での観測

- ・新潟や函館、静岡など

# 御前崎(静岡)観測し一ダ

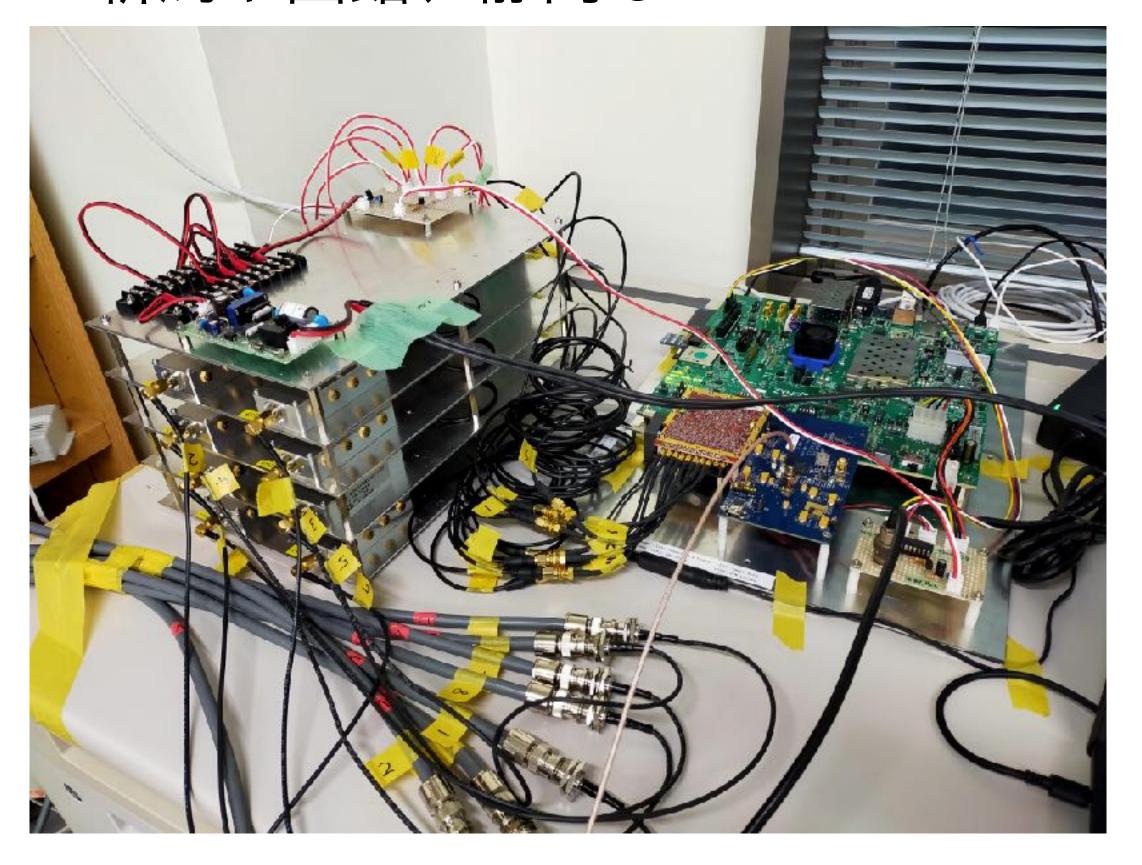

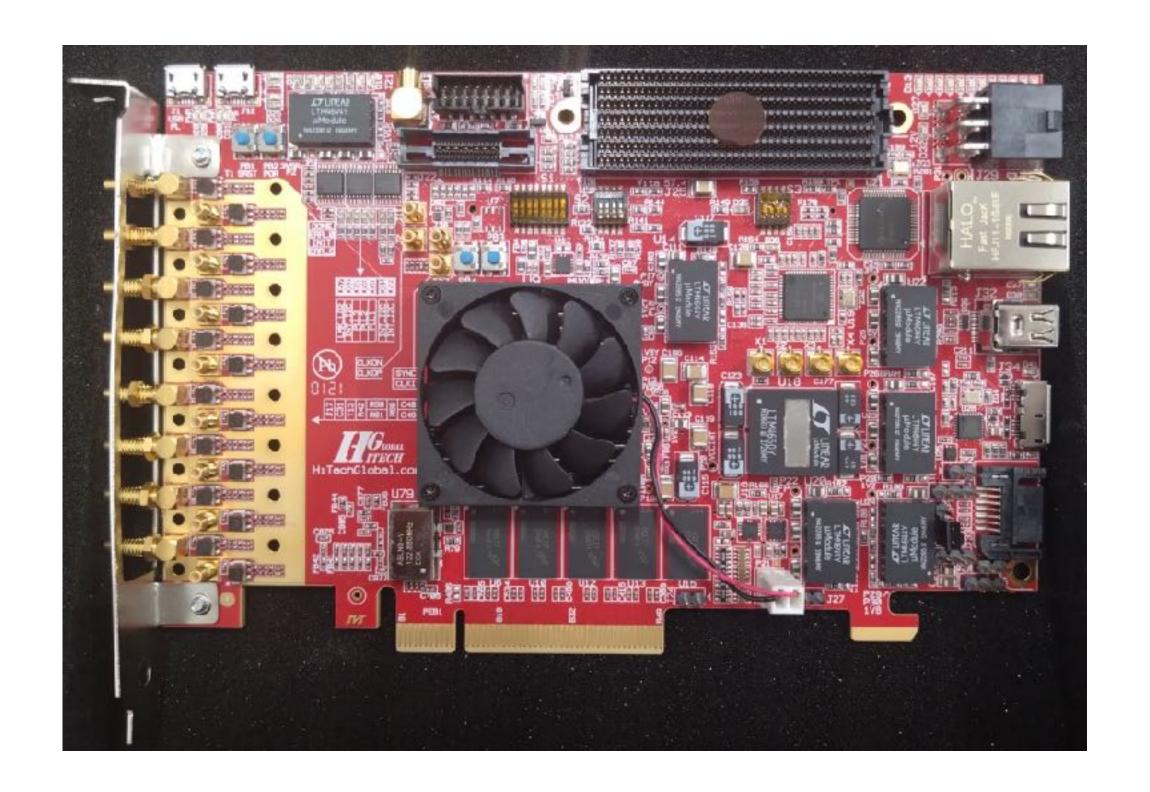

・ 以前運用していたボード

RFSoC 28DR (HitechGlobal ZRF-8)

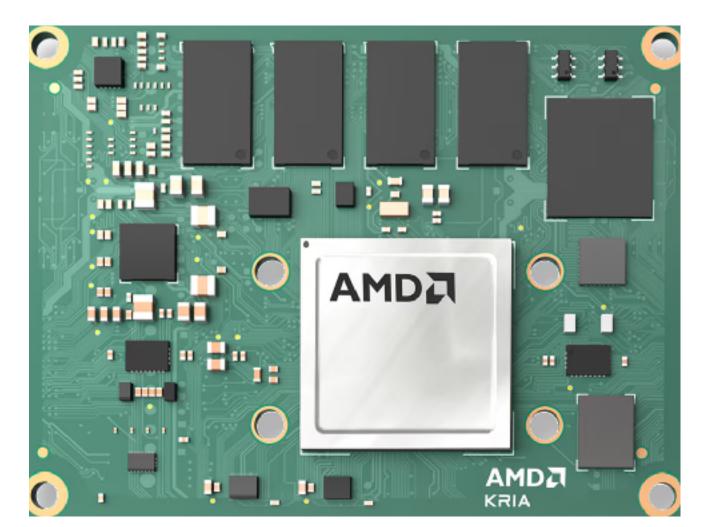

・現在運用中のボード

ORNIS ボード (Kria K26)

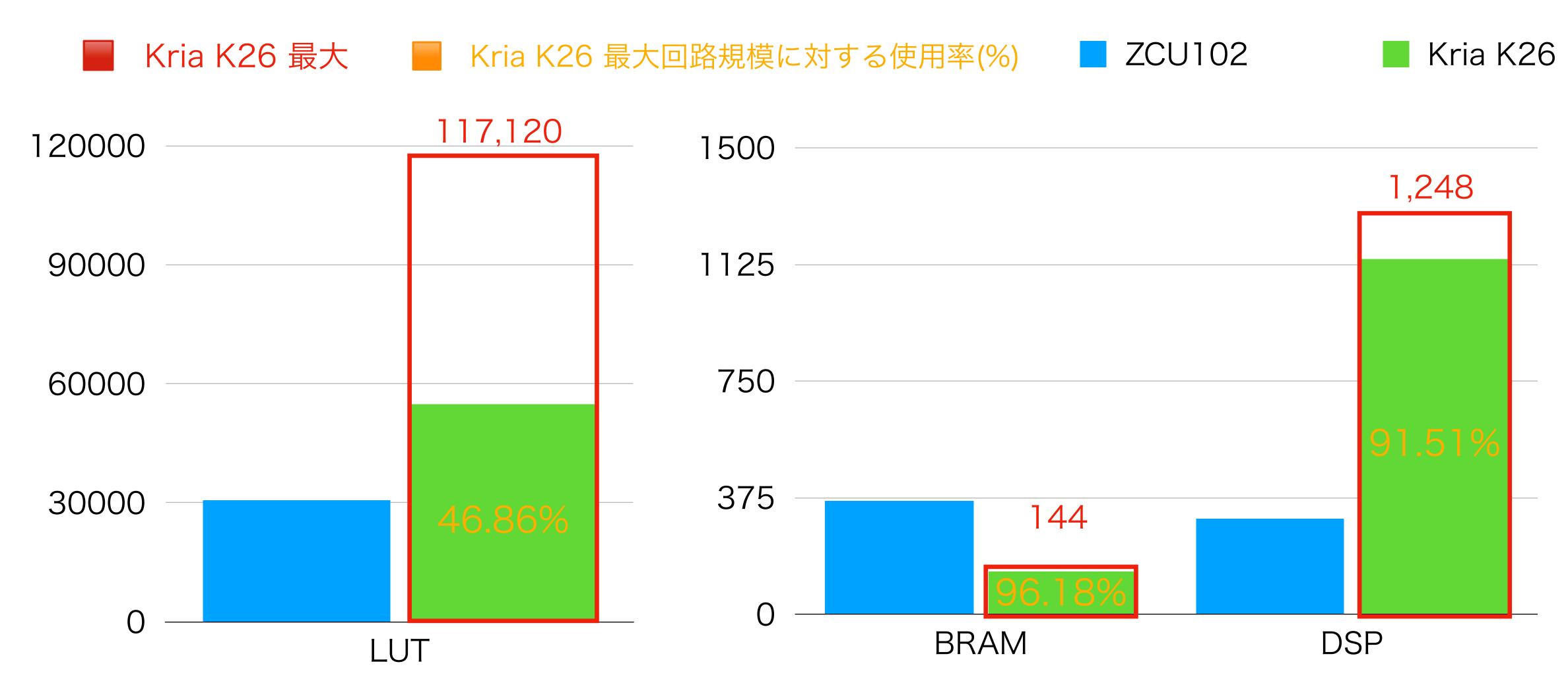

# ZCU102 と Kria K26 比較

| FPGA ボード | Price   | Device | LUT     | BRAM | DSP   |

|----------|---------|--------|---------|------|-------|

| ZCU102   | \$3,234 | ZU9EG  | 274,080 | 912  | 2,520 |

| Kria K26 | \$325   | ZU5EV  | 117,120 | 144  | 1,248 |

ZCU102

Kria K26

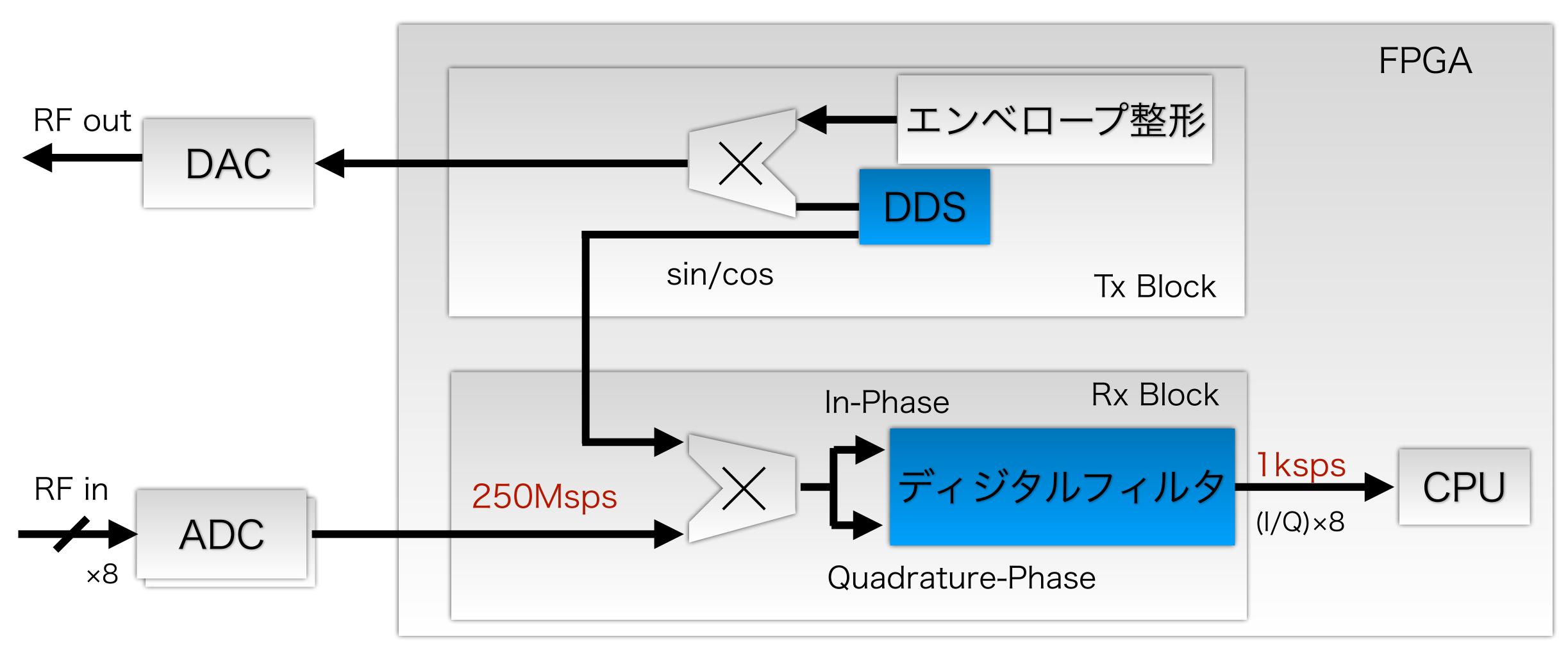

#### レーダ送受信機概要

# ディジタルフィルタ

| Filter                         | 長所                                                          | 短所                                                                       |  |  |

|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| (Infinite inpulse<br>Response) | から行                                                         | <ul><li>■ 係数によって不安定</li><li>■ 誤差が大きく現れる</li><li>■ 直線位相特性が実現不可能</li></ul> |  |  |

|                                | <ul><li>常に安定</li><li>直線位相特性が正確</li><li>誤差が大きく現れない</li></ul> | ■ 急峻な特性の実現には高次<br>のフィルタが必要                                               |  |  |

|                                | <ul><li>常に安定</li><li>低次のフィルタで狭帯域を<br/>実現</li></ul>          | ■ 他のフィルタを併用する必要がある                                                       |  |  |

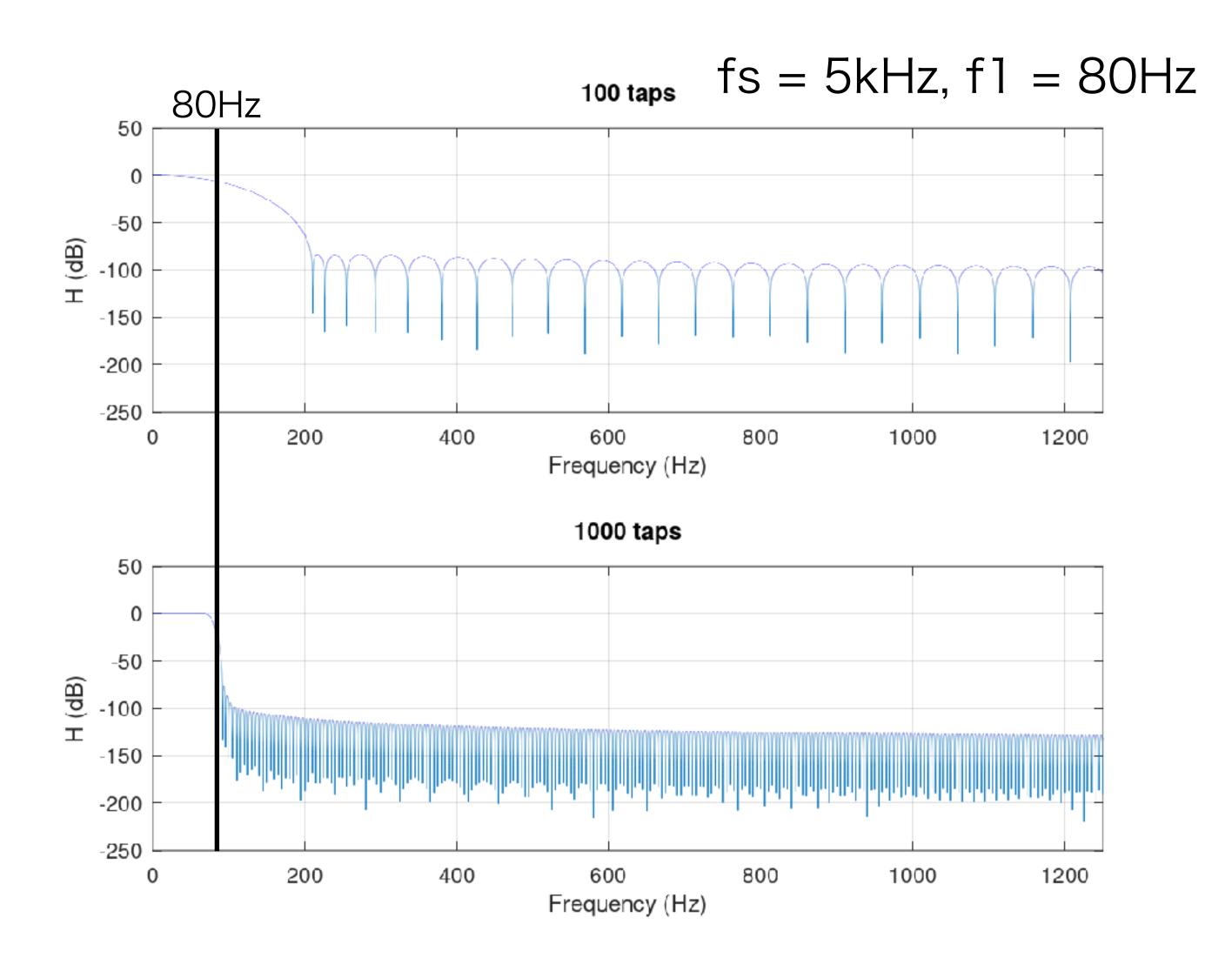

# FIR(Finite Impulse Response)

- 次数 = タップ数

- ・タップ数の増加

- フィルタ特性が向上

- ■回路規模の増加

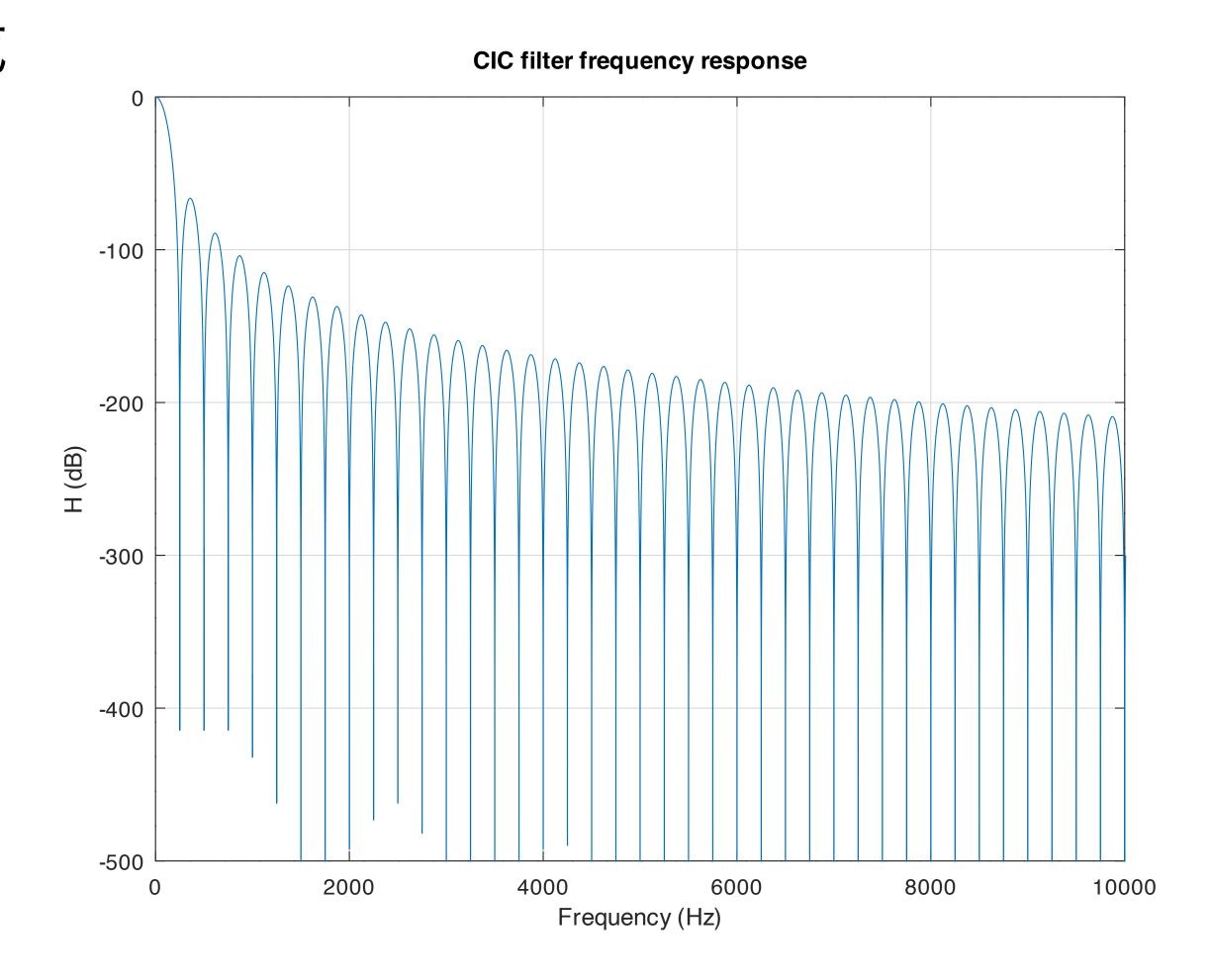

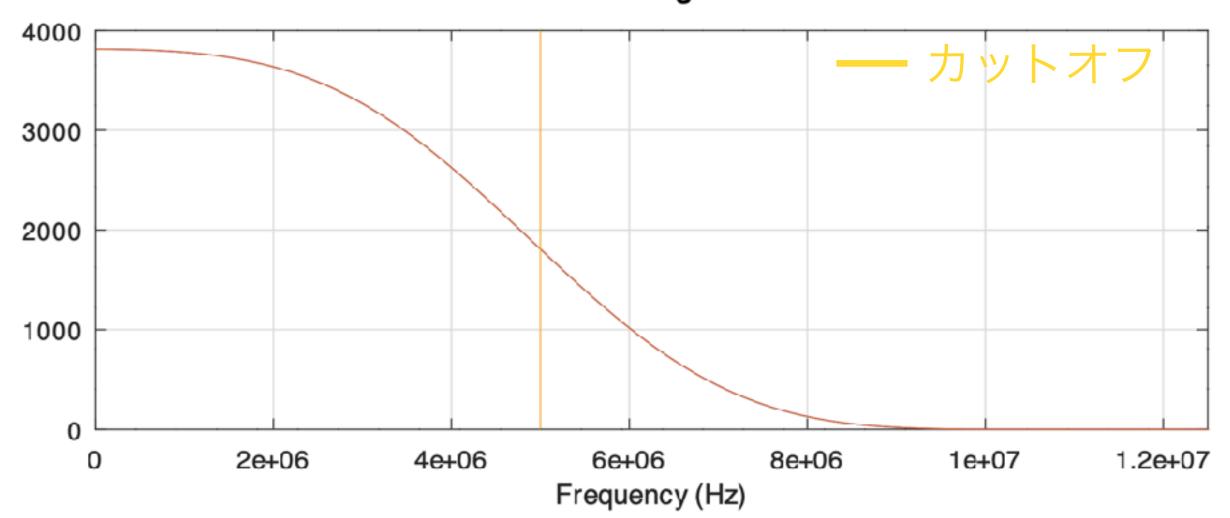

# CIC (Cascaded Integrator Comb)

- 低いタップ数で狭帯域のフィルタを作成

- ・回路規模を大きく削減可能

- フィルタ特性に問題

- ・ 跳ね上がりがある

- エイリアシングの発生

- FIR フィルタなどと併用し抑制

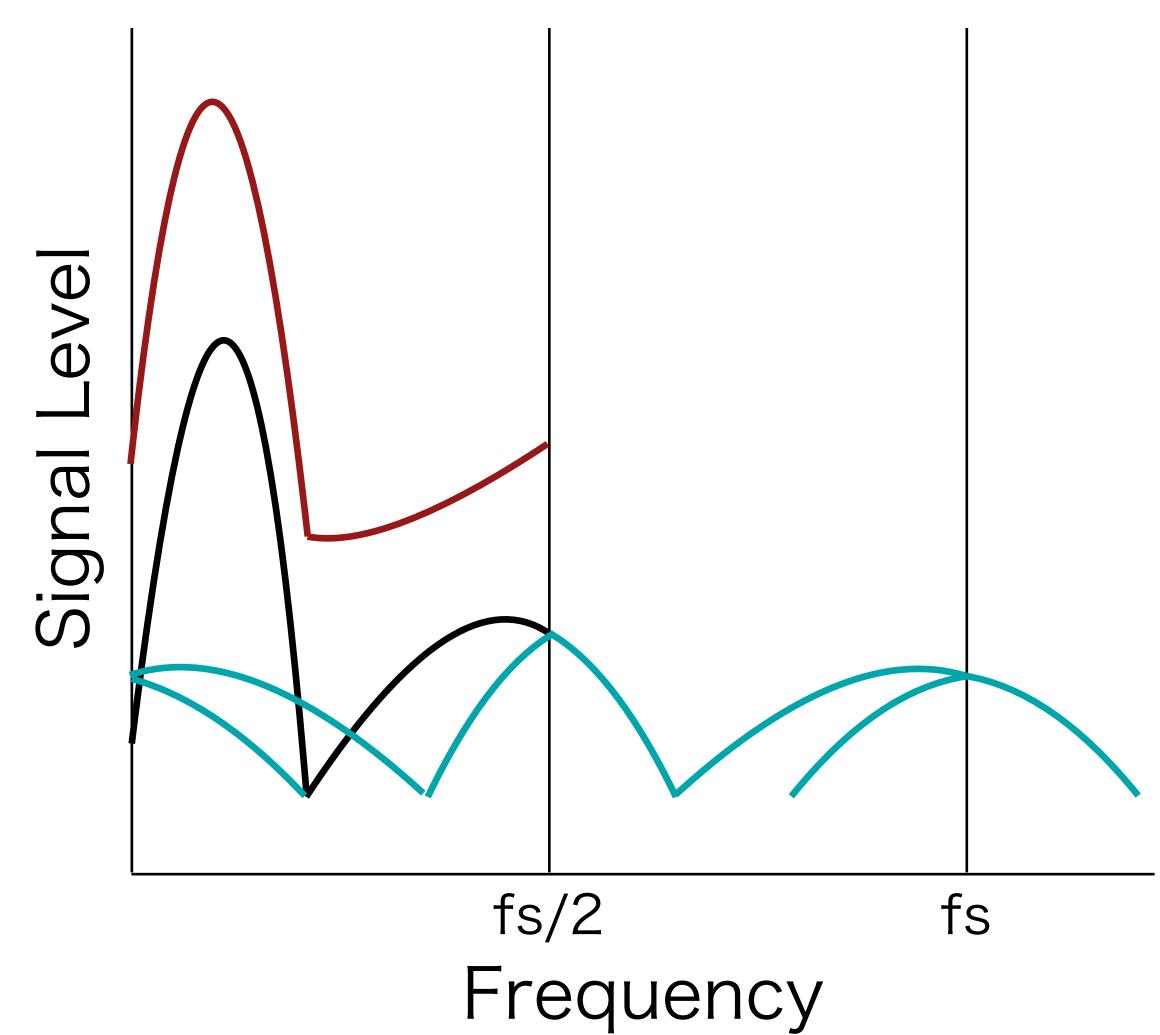

#### エイリアシング

fs: 出力サンプリングレート

- $f_s/2 f_s$

- fs/2 を対象に折り返す

- fs 以上

- OHz 付近に現れる

- ・ これら全てが加算

- ・赤色の成分として出力

# 従来(ZCU102)におけるフィルタ設計

| フィルタ    | f <sub>s</sub> (Hz) | R       | f <sub>1</sub> (Hz) | N   | LUT   | BRAM | DSP |

|---------|---------------------|---------|---------------------|-----|-------|------|-----|

| 1 (CIC) | 250M                | 1,000:1 |                     | 5   | 3,536 | O    | 64  |

| 2(FIR)  | 250k                | 25:1    | 1,500               | 512 | 2,000 | 144  | 112 |

| 3(FIR)  | 10k                 | 10:1    | 200                 | 512 | 4,800 | 120  | 112 |

fs:サンプリング周波数 R:デシメーション比 f1:カットオフ周波数 N:タップ数

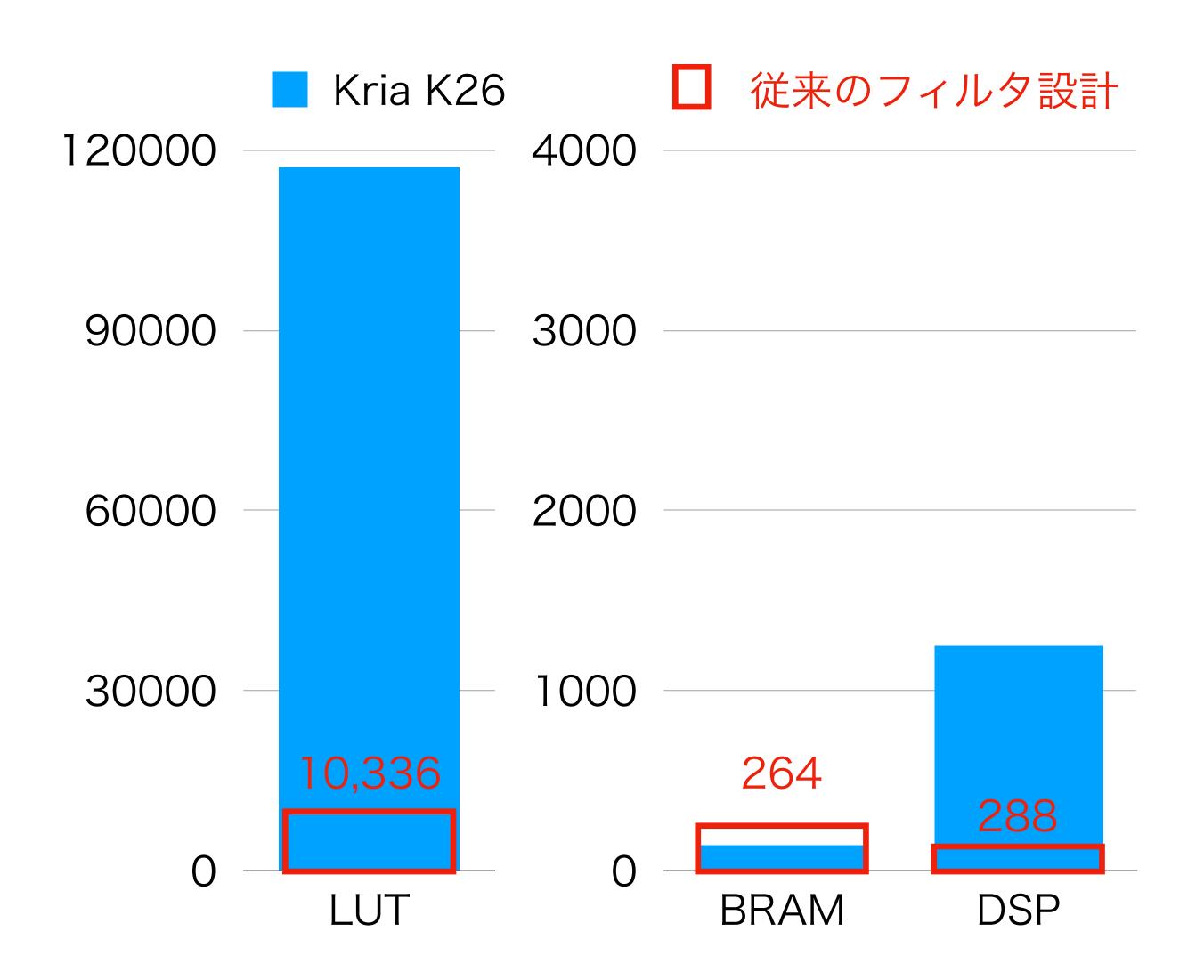

#### Kria K26 への実装

- ・従来のフィルタ設計のまま実装

- ・フィルタだけ

- 。 LUT と DSP は余裕がある

- BRAM が不足

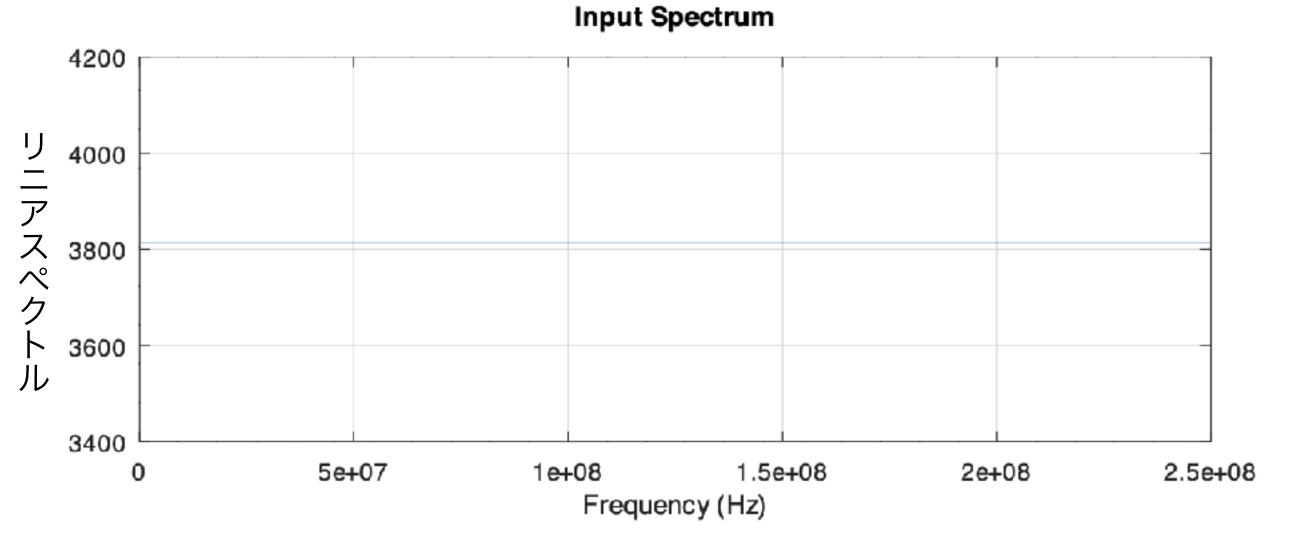

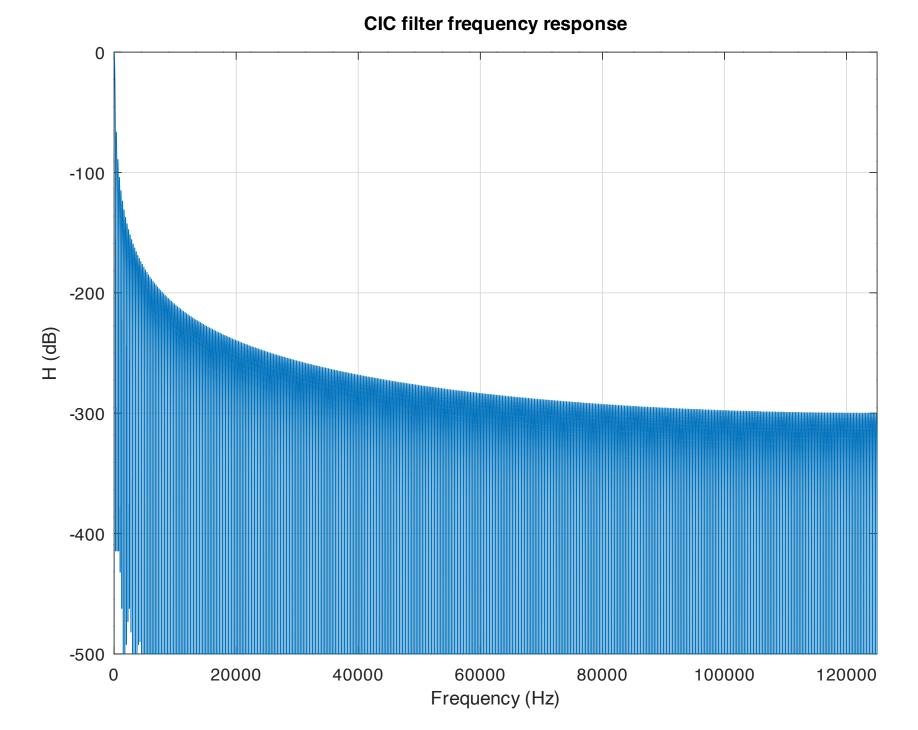

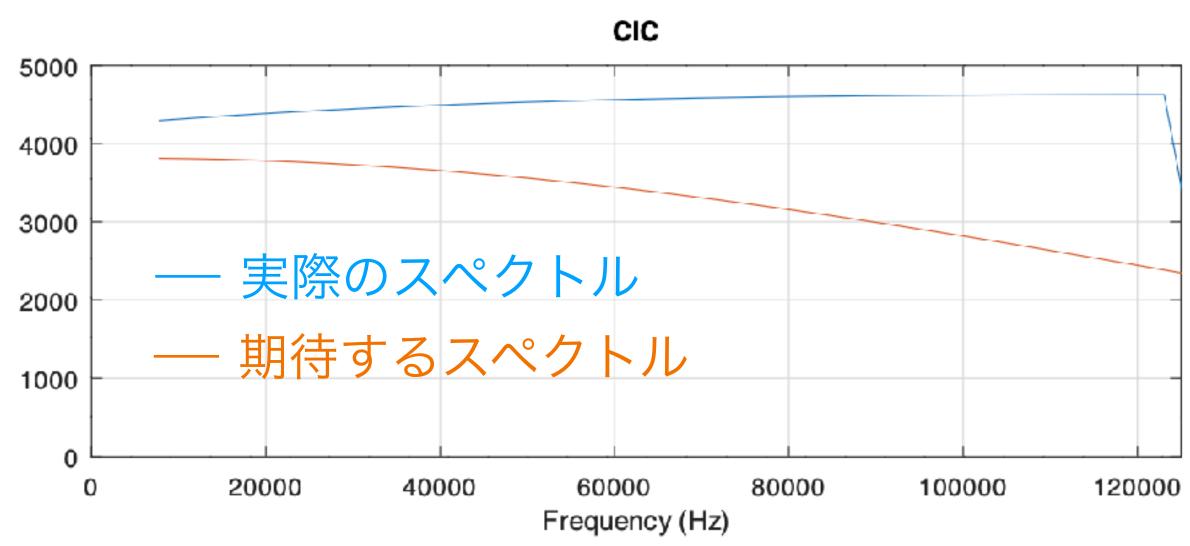

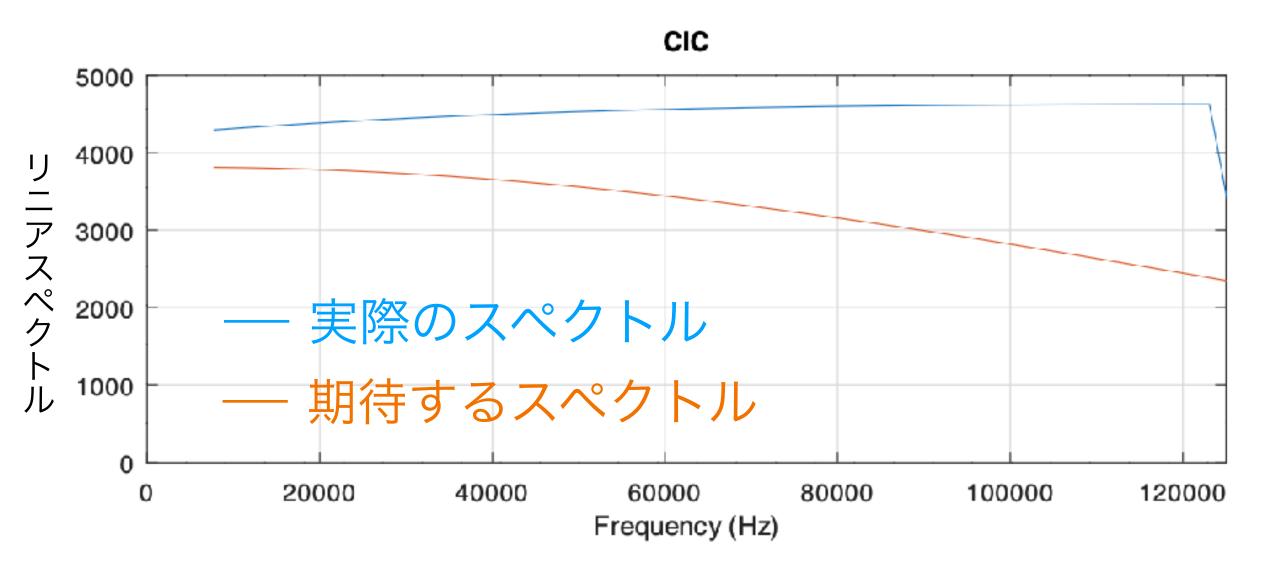

# CICによるエイリアシング

- 1段目の CIC による影響

- ・出力周波数の1/2を境として

- エイリアシングの発生

- 発生していない場合が橙色

入力スペクトル

CIC フィルタ特性

CIC 通過後のスペクトル

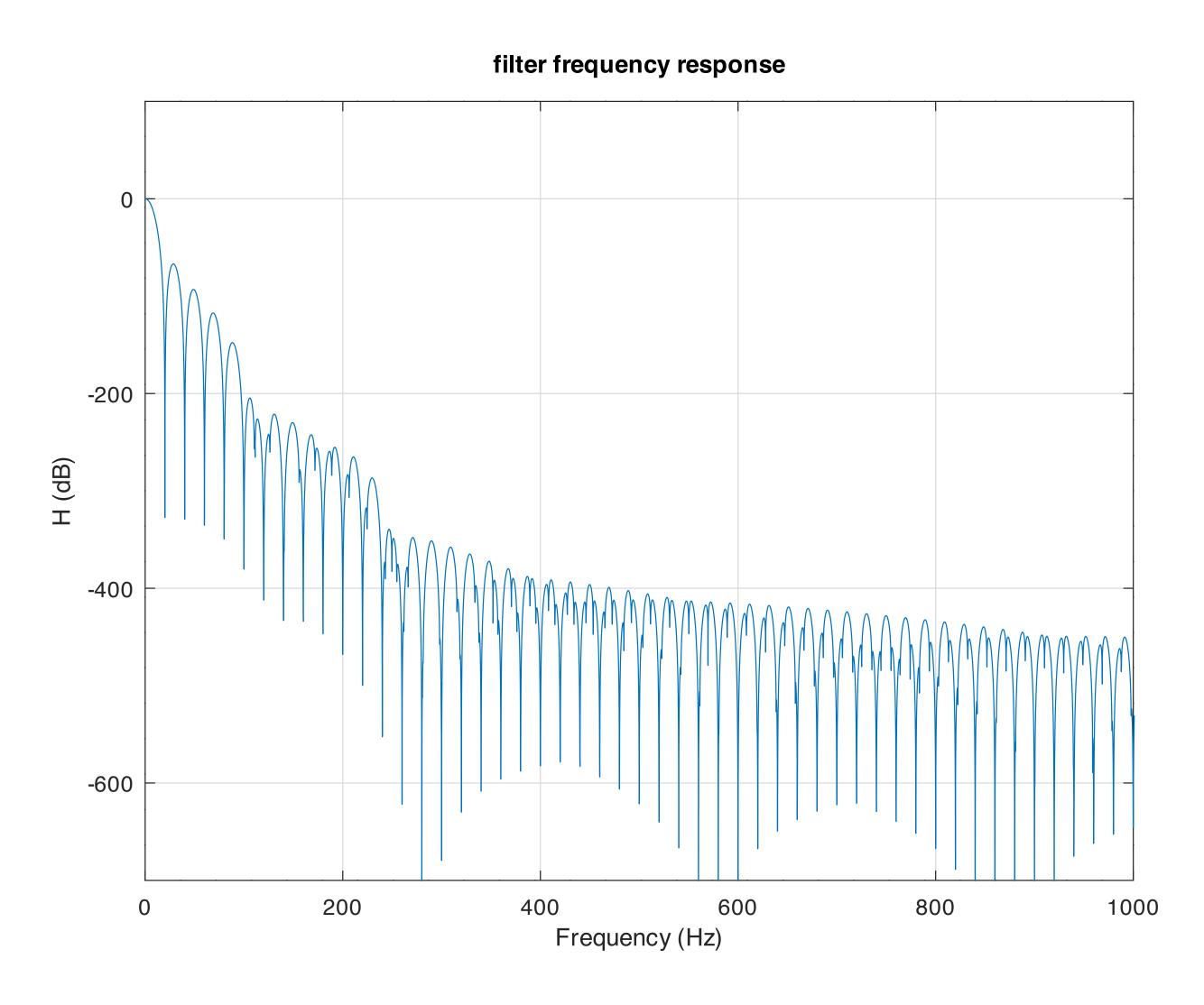

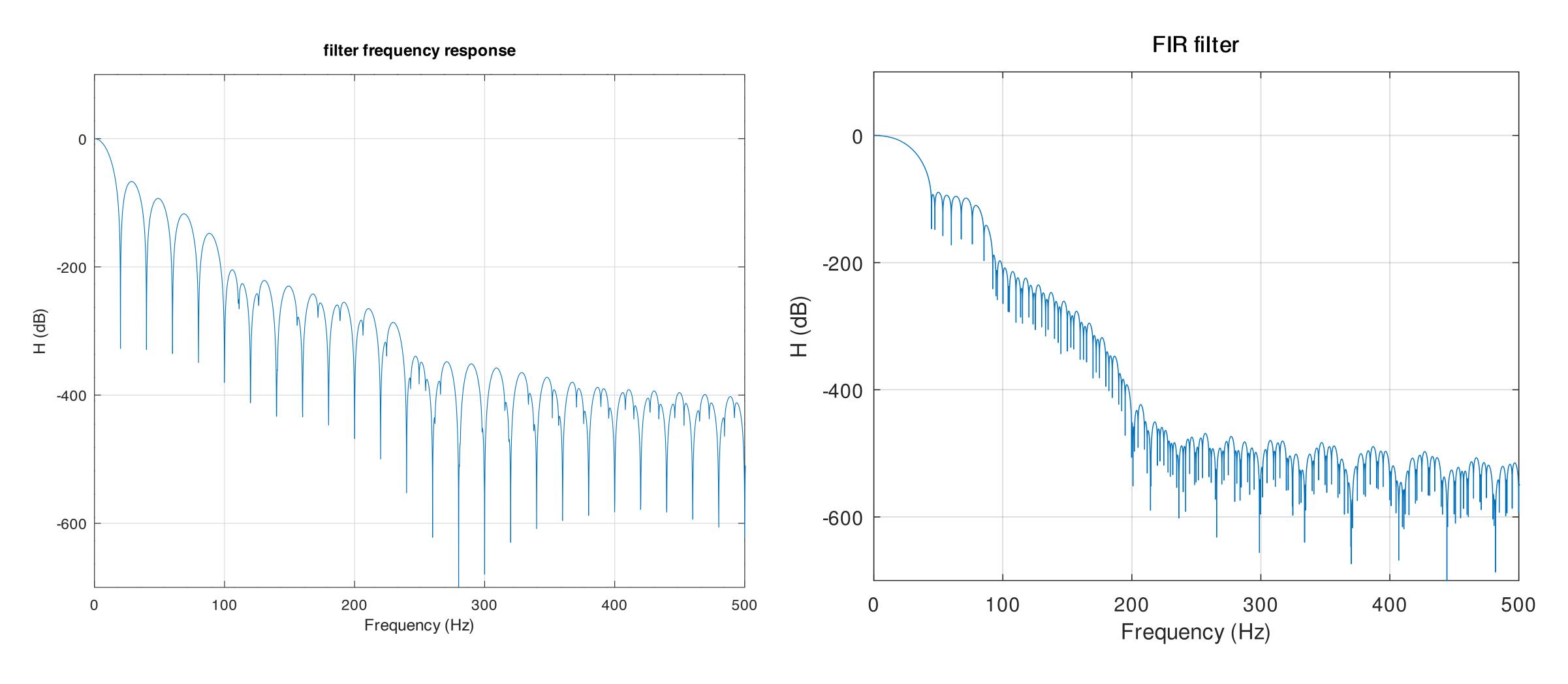

# 全体のフィルタ特性(ZCU102)

- ・ フィルタ全体のフィルタ特性

- ・ 3 段の周波数応答を掛け算

- 特性

- ・阻止域までなだらか

- ・ CIC の影響

- ・実際の観測においてのノイズ

- エイリアシングの影響

#### 理想的なフィルタと設計方針

- ・ 理想的なフィルタ

- 1. FPGA 変更後の回路規模に収まる

- 2. エイリアシングがない

- 設計方針

- ・CIC フィルタを除去し、FIR のみの構成とする

- ・エイリアシングをなくす

#### 最終的なフィルタ構成

| Stage | f <sub>s</sub> (Hz) | R    | f <sub>1</sub> (Hz) | N     | LUT    | BRAM | DSP |

|-------|---------------------|------|---------------------|-------|--------|------|-----|

| 7     | 250M                | 10:1 | 5M                  | 128   | 19,028 | 0    | 496 |

| 2     | 25M                 | 10:1 | 500k                | 128   | 6,600  | 32   | 112 |

| 3     | 2.5M                | 50:1 | 10k                 | 500   | 8,327  | 33   | 112 |

| 4     | 50k                 | 10:1 | 1,000               | 100   | 8,153  | 0    | 112 |

| 5     | 5k                  | 5:1  | 80                  | 1,000 | 6,404  | 33   | 112 |

fs:サンプリング周波数 R:デシメーション比 f1:カットオフ周波数 N:タップ数

#### FIRのエイリアシング

- ・従来との1段目の比較

- 折り返しがない

- fs/2 より十分下で落ちている

CIC 通過後のスペクトル

入力スペクトル

#### FIR Stage1

FIR 通過後のスペクトル

### 全体のリソース使用量

# 全体の周波数特性

#### まとめ

- ・ 海洋レーダ全国展開に向けて

- FPGA を用いたディジタル実装

- ・使用する FPGA ボードを低価格なものに

- FPGA 変更において

- ・デバイス規模縮小における回路規模最適化

- ・フィルタ設計の変更

- → 回路規模を抑え、エイリアシングの発生を抑制